### **Broadcom and Deutsche Bank Custom Silicon Teach-In**

April 19, 2022

### **Safe Harbor Statement**

This presentation contains forward-looking statements that are based on current expectations and beliefs of Broadcom management, assumptions made by and information currently available to Broadcom management, current market trends and market conditions that involve risks and uncertainties, many of which are outside Broadcom's and Broadcom management's control, and which may cause actual results to differ materially from those statements. Many of these risks and uncertainties are and will be exacerbated by the COVID-19 pandemic and any worsening of the global business and economic environment as a result.

Our filings with the SEC, which you may obtain for free at the SEC's website at <a href="https://www.sec.gov">https://www.sec.gov</a>, discuss some of the important risk factors that may affect our business, results of operations and financial condition. Actual results may vary from the estimates provided. We undertake no intent or obligation to publicly update or revise any of the estimates and other forward-looking statements made in this presentation, whether as a result of new information, future events or otherwise, except as required by law.

# **Broadcom Speakers**

Hock E. Tan

President & CEO

Frank Ostojic SVP & GM, ASIC Products

Vijay Janapaty

VP & GM, Physical

Layer Products

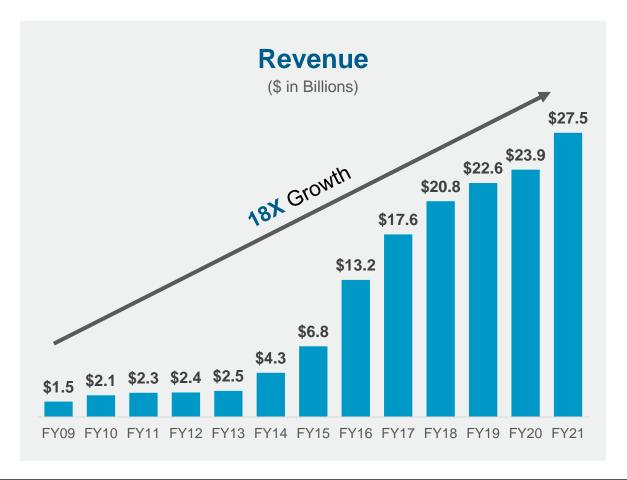

# How Broadcom Became a Global Technology Leader

Category-Leading Franchises: 8 in 2009 → 22 Today

177X Growth in Operating Profit from 2009 → 2021

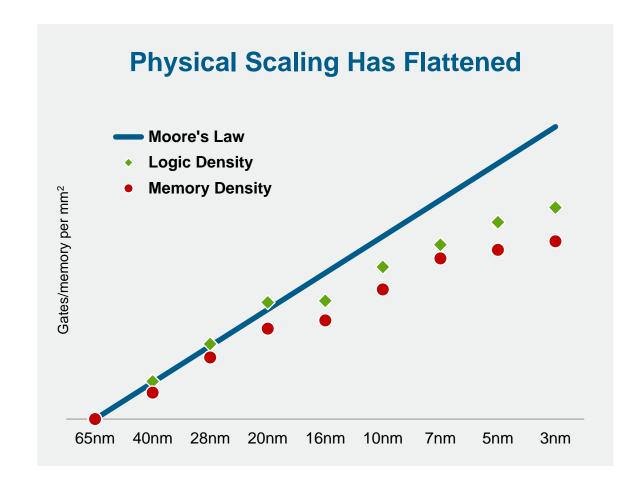

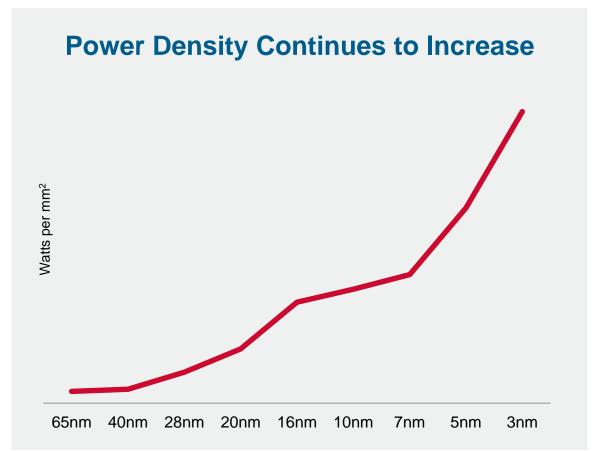

### Moore's Law Has Ended!

Source: Broadcom data and estimates

# **Need New Approaches to Chip Development**

### **Are We on a New Growth Trajectory?**

Frank Ostojic – SVP & GM, ASIC Products

Vijay Janapaty – VP & GM, Physical Layer Products

### Foundation for Successful Silicon Innovation

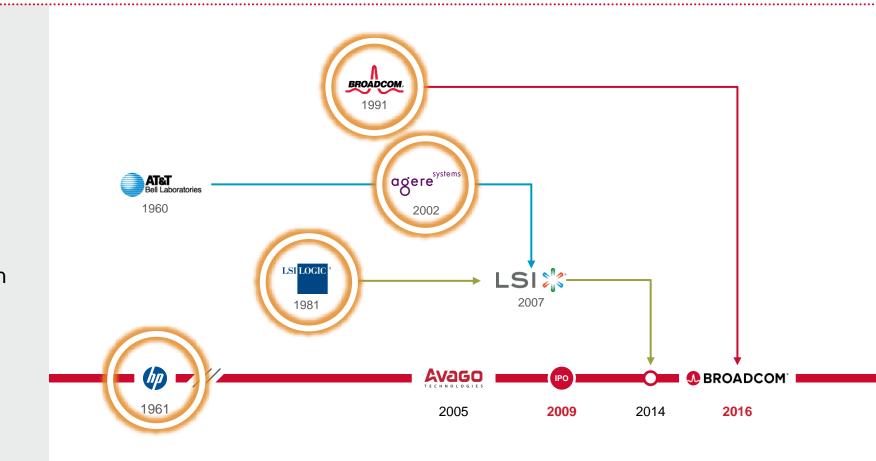

# **Custom ASICs Heritage, 3 Decades of Custom ASICs Experience**

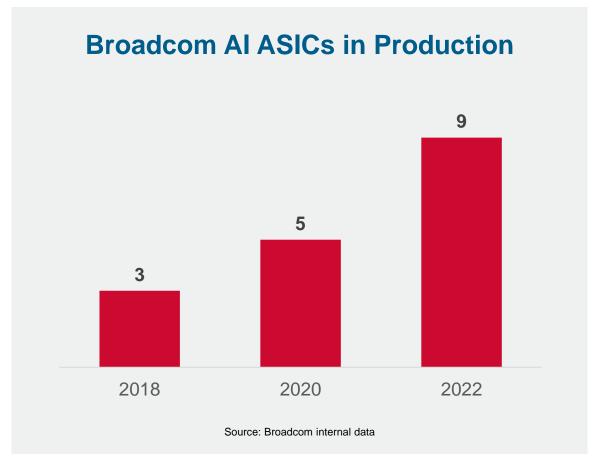

# Broadcom ASIC Products Division

- The combination of 3 large ASIC groups: Avago + LSI + Agere

- Has been developing Custom Silicon for over 30 years across 10+ technology generations (0.35um to 3nm)

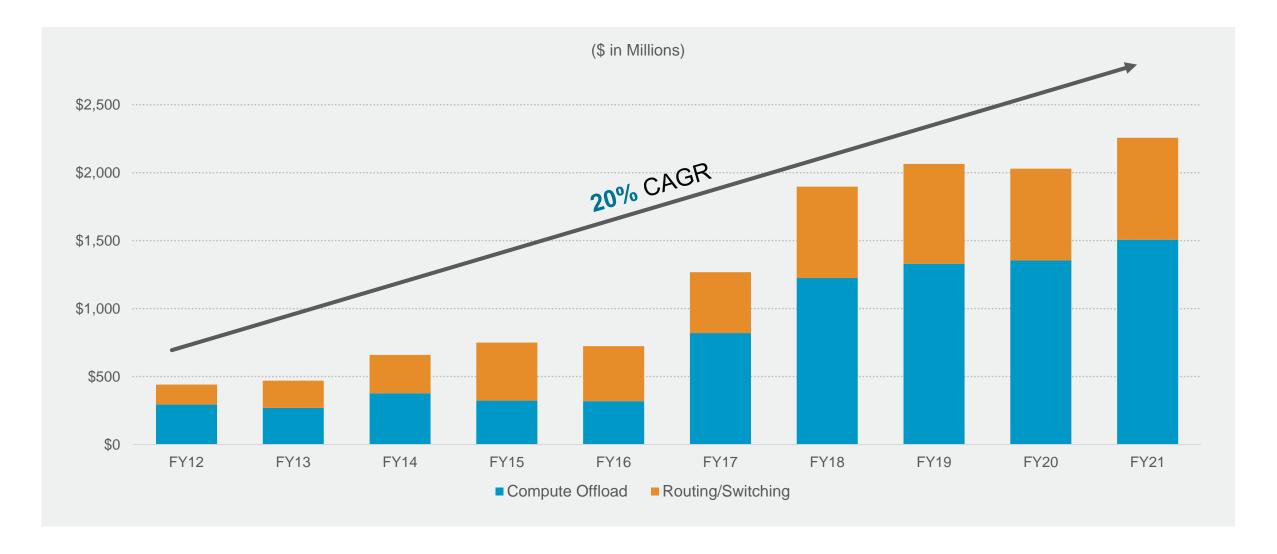

# **Custom ASIC Revenue by End Market**

# **Custom ASIC Revenue by End Market**

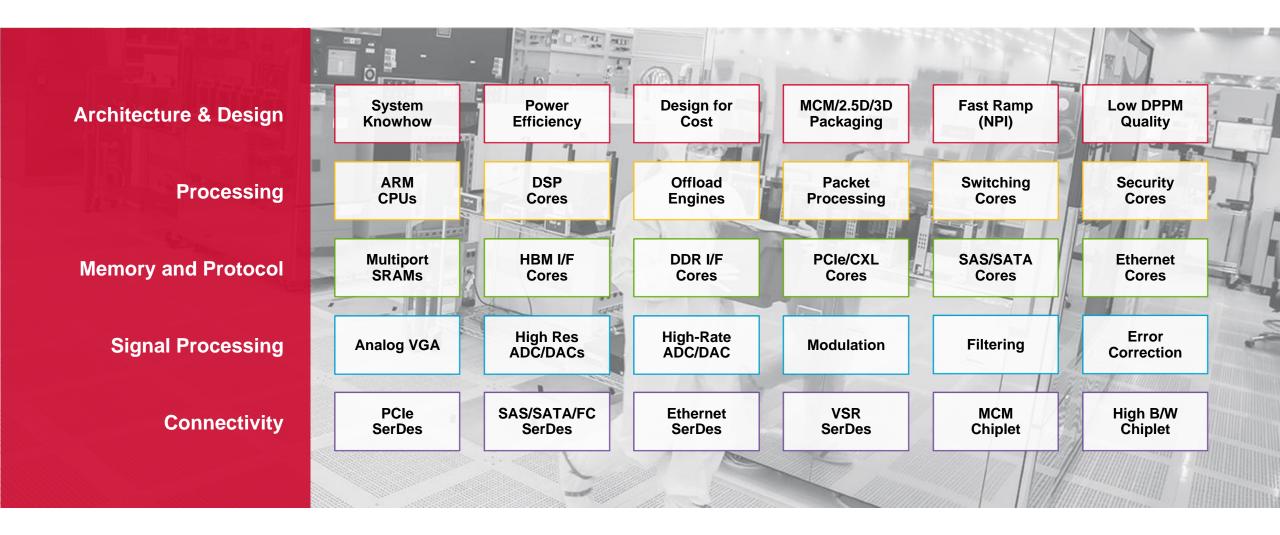

# **Broadest Silicon Capabilities**

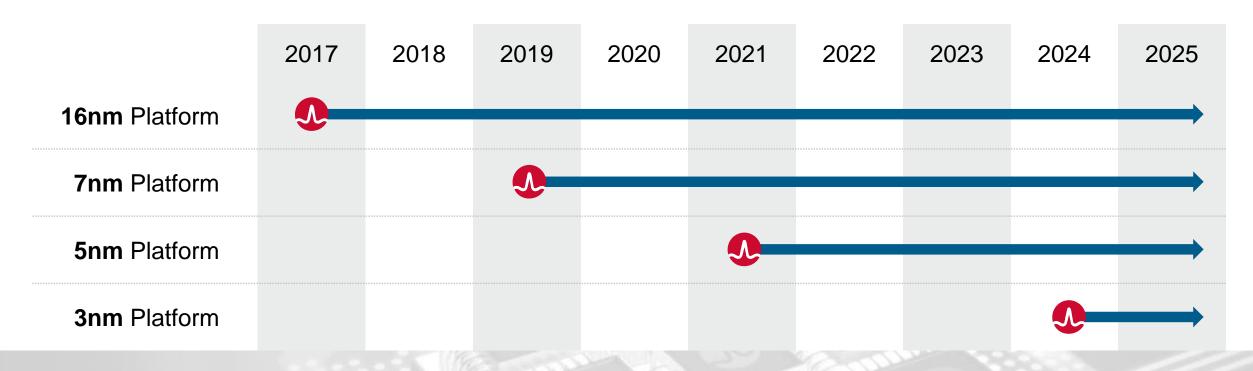

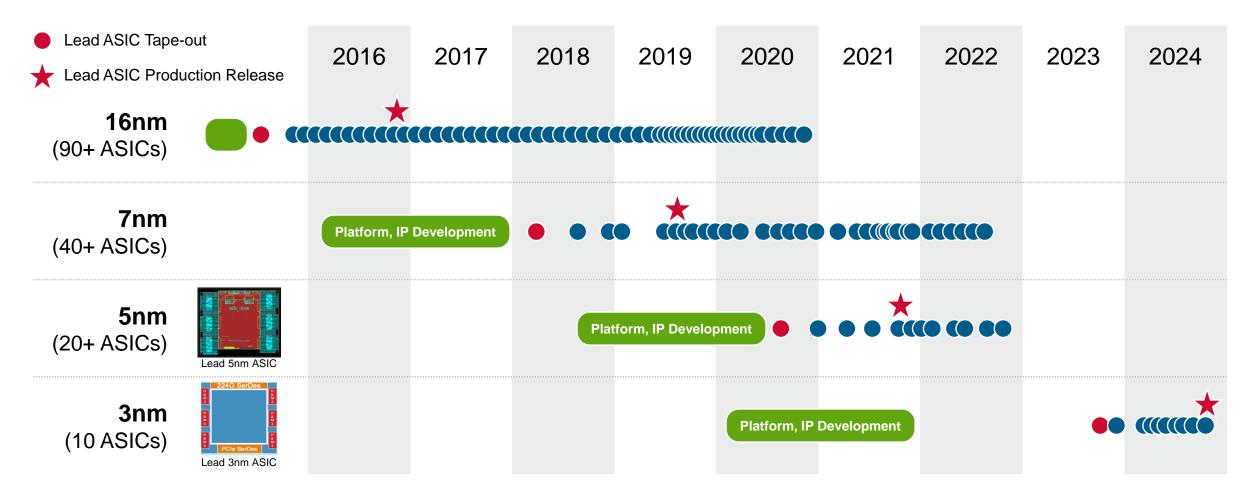

# **Leading Edge Silicon Platform Cadence**

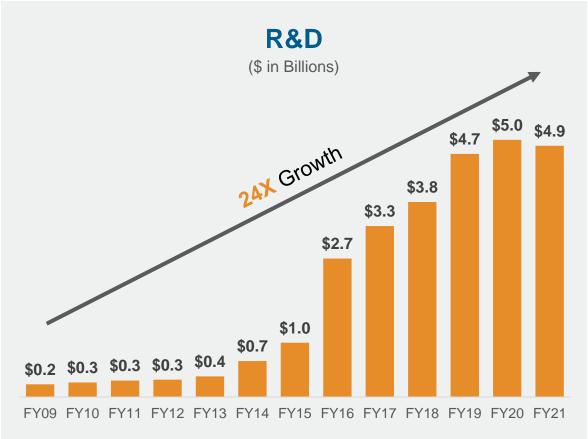

### **Broadcom's R&D Platform Scale Drives Innovation**

### Scale of the Broadcom ASIC Machine

- Investment scale enables the development of a new Technology Platform ~ every 2 years in alignment with Foundry

- R&D scale, combined with efficient design methodology, enables the development of ~60 ASICs at a given time

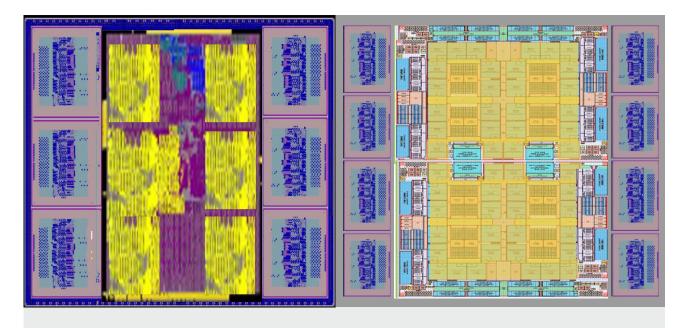

# **Proven Methodology for Very Complex SoCs**

# A Predictable ASIC Machine \*\*BROADCOM\*\* \*\*

- Designs in future generations will double current complexity

- Packaging and thermal technology leadership

→ integration in complex SoCs

### **Design Parameters**

- Die sizes of 600 to 800 mm²

- 60B 110B+ transistors in core die

- 96 GB 128 GB of HBM capacity

- ~30 Tb 50 Tb of network bandwidth

- Multiple die integrated in 2.5D packaging technology

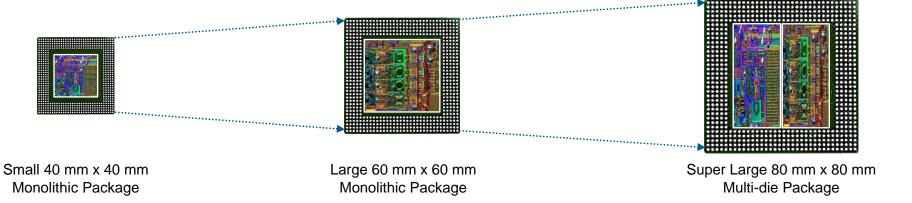

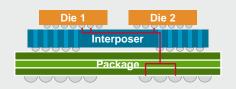

# **Packaging Technology Leadership**

Increasing SoC design content and size, coupled with a slowing of silicon area scaling, has led to a renaissance in packaging technology

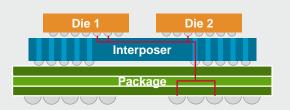

**Evolution of 2D Packages**

**Evolution of 2.5D, 3D Packages**

Si Interposer up to 1600 mm<sup>2</sup>, Package Size 80 mm x 80 mm

Si Interposer up to 3200 mm<sup>2</sup>, Package Size 100 mm x 100 mm

Si Interposer up to 3200 mm<sup>2</sup>, Stacked Die, Package Size 100 mm x 100 mm

# **Hyperscale Accelerator Examples**

**New Growth Market for Custom Silicon**

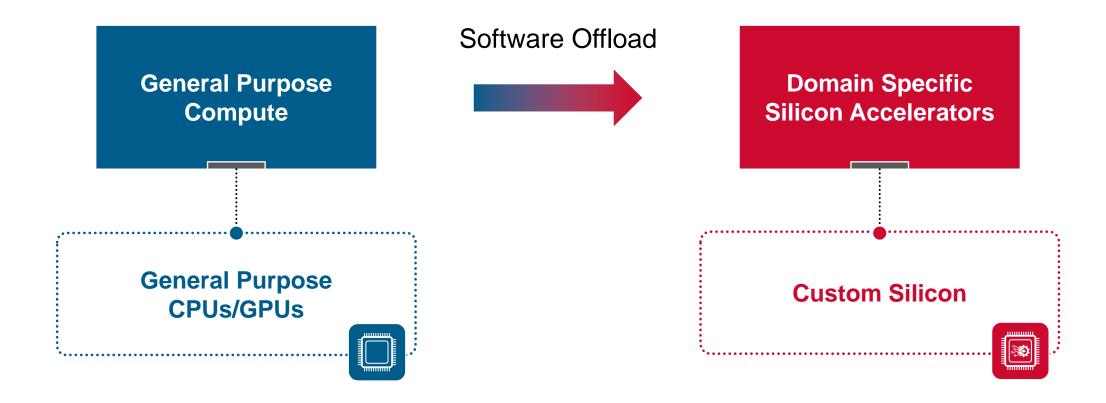

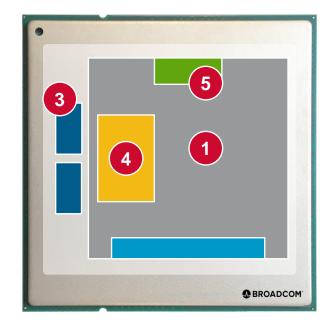

### **AI Custom Silicon**

- 1 Matrix multiply/accumulate (5nm/3nm Libs/memories)

- 2 Network connectivity (800 Gbps/1600 Gbps links)

- 3 Die-to-die interconnect (10+ Tbit/s)

- 4 High bandwidth memory (HBM2e/3)

- 5 Advanced packaging (2.5D CoWoS)

- 6 First to market, fast NPI

### **Most Complex Custom Silicon**

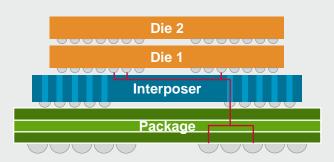

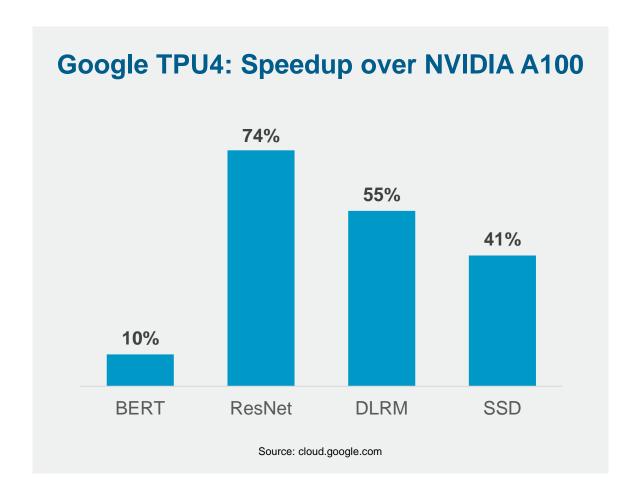

# **Domain Specific Architectures Outperform GPUs/CPUs**

### **Higher Performance and 20%+ Lower Area and Power**

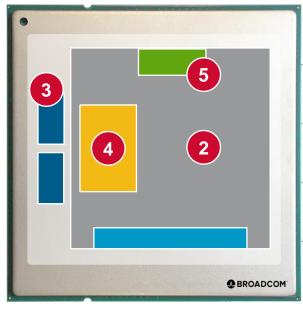

### **Datacenter Accelerators**

SmartNIC or DPU

Video Acceleration

- 1 Virtualization, security, protocol offload (5nm/3nm)

- 2 Video codecs offload (5nm/3nm)

- 3 High bandwidth memory (HBM2e or DDR5)

- 4 CPU subsystem (ARM)

- 5 Network connectivity (800G links)

Benefits: Virtualization, Video, Protocol, Security Offloads and DC Orchestration

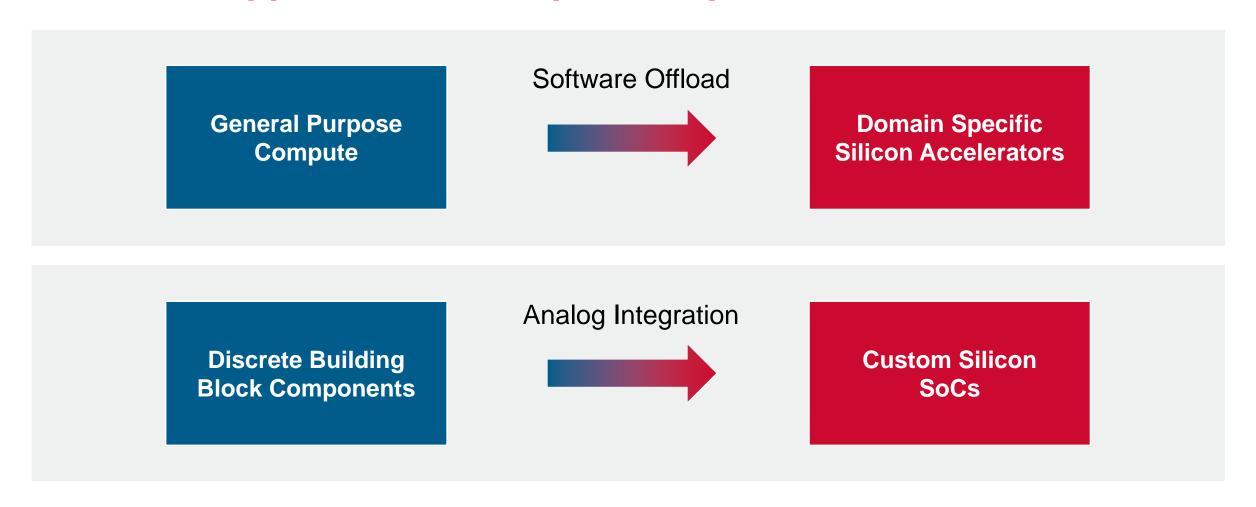

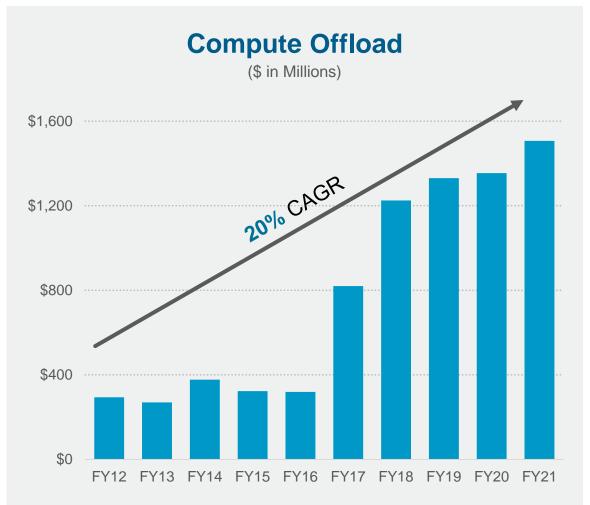

### Hardware Accelerators Replace Software/CPU

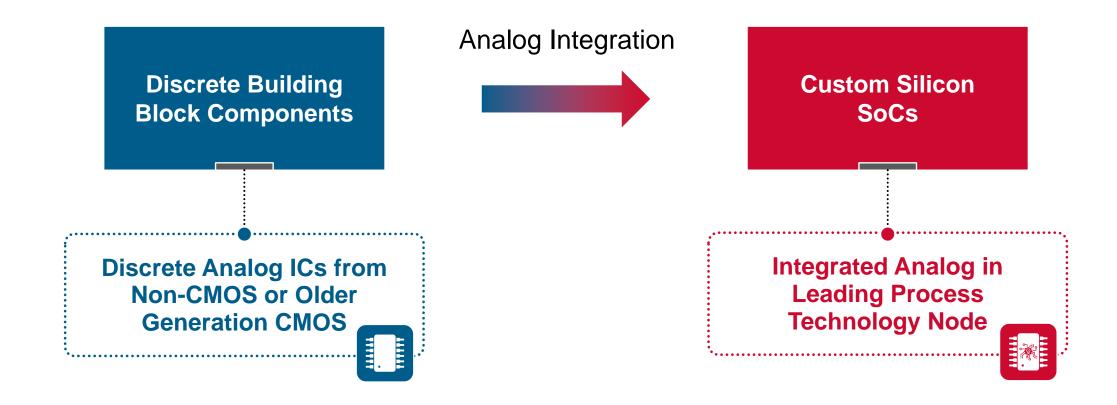

# **Horizontal Integration**

### **Integration Drives Content Growth**

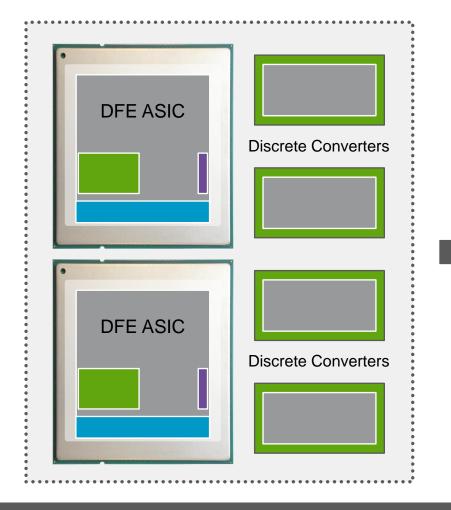

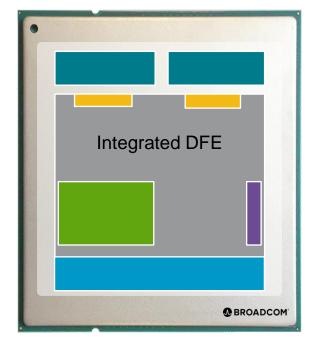

## 5G Radio: Bandwidth Increase, Power & Cost Reduction

- Integrated DFE and AFE

- Direct RF, DSP centric AFE

- 5G-advanced support

- BW > 800 MHz, dual-band TRXs

- 25%+ FE power reduction

- Antenna weight reduction

- Radio SKU reduction

DFE = Digital Front End

AFE = Analog Front End

BW = Bandwidth

TRX = Transceiver

**5G Operator CapEx and OpEx Reduction**

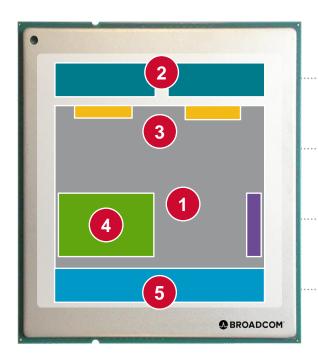

### **5G Massive MIMO Radio Silicon**

- 1 Power efficiency (5nm/3nm libraries/memory)

- 2 Data converter chip-let (5nm direct RF, 5G-Adv, 800 MHz+)

- 3 Die-to-die interconnect (high bandwidth, low power chip-lets)

- Protocol and control plane (Integrated ARM & DSP subsystems)

- Baseband connectivity (CPRI, eCPRI interfaces)

First to Market: Direct RF Data Converters in 5nm

**Custom 5G Radio SoC Opportunity = \$1.2B SAM in CY24\***

<sup>\*</sup> Based on Dell'Oro January 2022 and Broadcom estimates

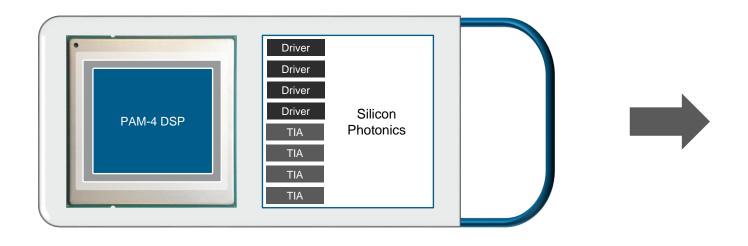

# Data Center Interconnect: Integrated PAM-4 DSP

PAM-4 DSP Opportunity = \$800M SAM in CY24\*

Jesko

400G

Integrated PAM-4 DSP

with Driver

and TIA

Silicon

**Photonics**

Discrete DSP, TIA, and Driver

**Higher Power Dissipation**

Integrated DSP Solution

400G DR4 Module < 7W

800G DR8 Module < 14W

### **Integration Drives 25% Power Reduction**

<sup>\*</sup> Based on LightCounting September 2021 and Broadcom estimates

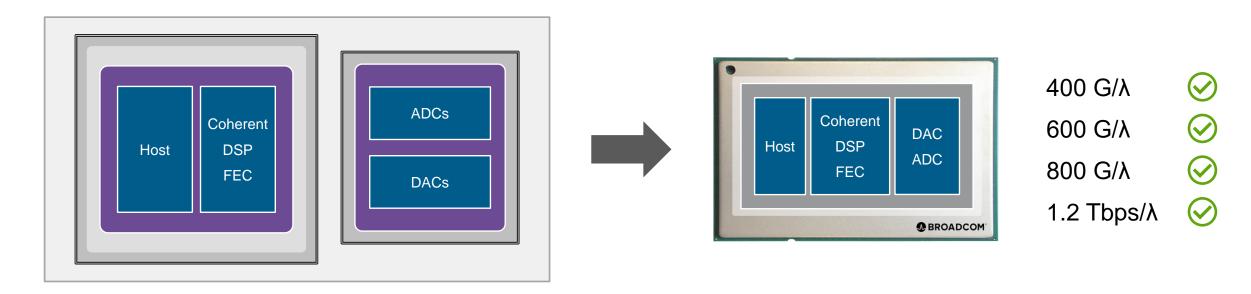

# **Transport and Routing Network (Coherent DSP)**

Discrete DSP and ADC/DAC Silicon

Limited Form Factors, Higher Power

# Integrated DSP → Unified IP Transport WAN DCI

Routing

...

### **Coherent DSP Opportunity = \$400M SAM in CY24\***

<sup>\*</sup> Based on Broadcom estimates

# **Key Takeaways**

Hyperscale accelerators offload software complexity to custom ASICs

Integration of discrete analog ICs drives custom silicon content growth

Broadcom is the #1 custom ASIC provider in infrastructure

Broadcom has a rich heritage of successful execution

Breadth of IP cores + leading edge silicon platform + proven design methodology